探索发现 · 交大智慧

探索发现 · 交大智慧

det365手机版_365正规网站是多少_365app下载手机版毛志刚团队在集成电路设计领域顶级会议ISSCC 2023发表最新研究成果

近日,上海交通大学电子信息与电气工程学院微纳电子学系毛志刚教授、何卫锋教授团队在2023年国际固态电路会议(International Solid-State Circuits Conference,ISSCC)上发表了题为“CCSA: A 394TOPS/W Mixed-Signal GPS Accelerator with Charge-Based Correlation Computing for Signal Acquisition”(CCSA:一种基于混合信号电荷域计算技术的高能效GPS信号捕获电路)的研究论文。

该研究通过采用数模混合的计算方式与电荷共享的累加机制,设计了一款新型GPS信号捕获芯片,其能效可达114-394TOPS/W,较现有国际最好水平提升了8.2倍。该论文的第一作者为微纳电子学系博士生李婕妤,通讯作者为其导师何卫锋教授。

研究内容

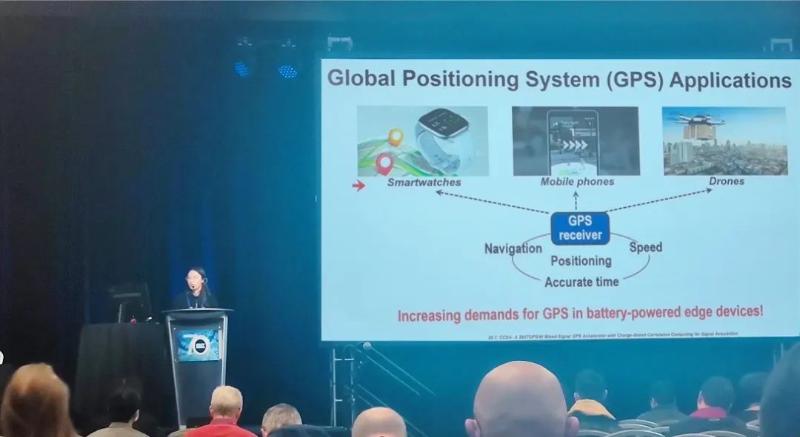

作为物联网和可穿戴计算设备中的核心模块,GPS(Global Positioning System, GPS)信号捕获电路的设计技术一直受到大家的关注。GPS接收机通过执行计算密集型的卷积相关操作来获取卫星信号与本地设备间的时间偏移量,从而完成本地位置的估算。为提高定位的准确性,GPS接收机通常需要针对多颗卫星(4~12颗)进行多次相关操作。在此情况下,信号捕获电路的能耗给便携式设备的续航工作能力带来了极大挑战。

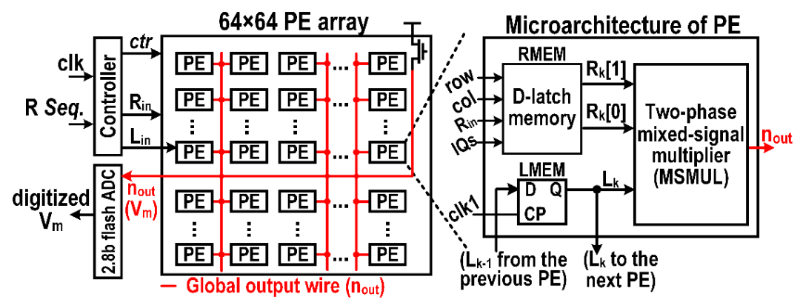

图1 GPS信号捕获芯片的顶层结构

研究团队针对卫星信号捕获过程中大量的相关操作,将乘法运算采用数模混合的方式实现,并将累加运算搬移到电荷域完成。在此基础上,通过采用大规模的并行执行阵列结构,有效提升了电路的计算性能和能效。图1给出了围绕上述思路所设计的二维大规模并行运算阵列(64Х64 PE)结构。

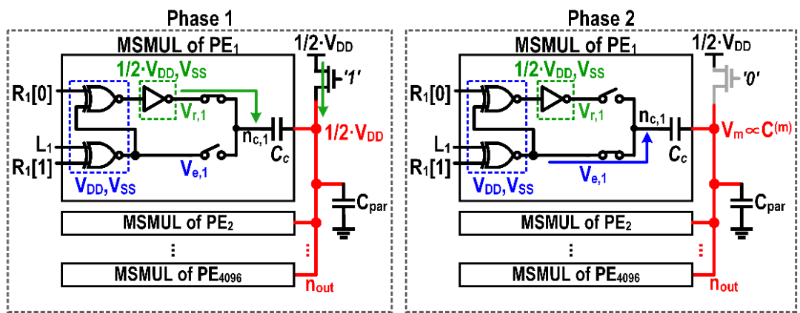

图2 混合信号乘法器结构及两相运算操作

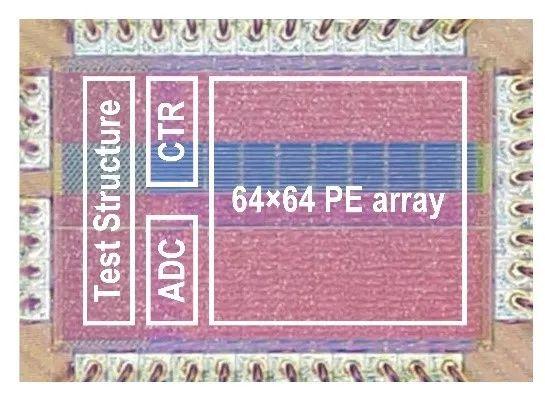

图3 GSP信号捕获芯片的显微照片

图2给出了所提出的混合信号乘法器(MSMUL)结构。基于上述结构,研究团队采用28nm工艺完成了信号捕获电路的芯片实现和流片验证,芯片显微照片如图3所示。

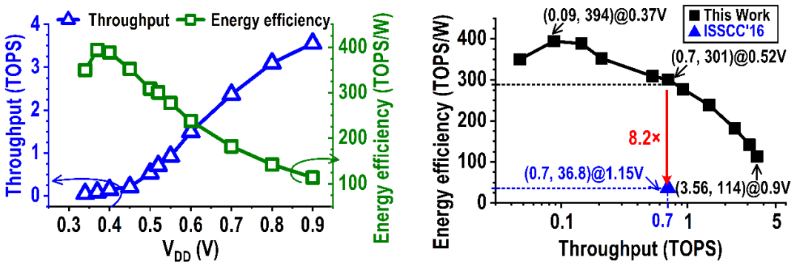

图4 GSP信号捕获芯片的测试结果

测试结果(图4)表明,该芯片可在0.34V至0.9V工作电压下实现114-394TOPS/W的计算能效。与国际现有最好水平相比,信号捕获电路的能效提升了8.2倍,吞吐率提升了5.2倍。该研究成果可显着提升智能手环、运动手表等穿戴设备的续航工作时间,对功耗受限的便携式计算设备在复杂应用场景下的快速GPS响应有着重要意义。

关于ISSCC

ISSCC(International Solid-State Circuits Conference 国际固态电路会议)是世界学术界和工业界公认的集成电路设计领域的最高级别会议,代表着国际的最高学术/技术水平,被称为集成电路设计领域的“世界奥林匹克大会”。

近年来,det365手机版_365正规网站是多少_365app下载手机版电院微纳电子学系立足国家战略需求,以尖端芯片设计技术探索为己任,在低功耗数模接口电路、高可靠片上网络芯片和高能效处理电路等方面分别取得突破,成果陆续发表在ISSCC上。

李婕妤在ISSCC 2023现场作报告

高能效GSP信号捕获芯片的技术研究得到了国家自然科学基金、科技部重点研发计划等项目资助。同时,归芯科技的李宜和冒小建博士也在芯片设计过程中给予了重要帮助。

高能效数字芯片设计团队的部分成员

(左起:何卫锋,李婕妤,毛志刚)